| 3차원 적층구조 소자 전력 분석 방법

| 문서번호 | PLA01201701 | 작성일 | 2017. 06. 07 |

| 소속 | 고려대학교 | 담당자 | 정성우 |

| 연락처 | 010-9100-3194 | 이메일 | swchung@korea.ac.kr |

[ 공 정 규 격 서 ] |

|||

| 공정명 | 3차원 적층구조 소자 전력 분석 방법 | 공정분류 | 분석 방법 |

| 1. 공정 목적 및 용도 | |||

|

○ 공정 목적 : 3차원 적층 (TSV 기반 3차원 적층 혹은 M3D 적층) 구조 소자의 전력소모를 전산모사를 통해 분석함으로써 전력소모를 최소로 할 수 있는 최적 구조의 설계에 도움을 줌 ○ 공정 용도 : 3차원 적층 (TSV 기반 3차원 적층 혹은 M3D 적층) 구조 소자의 전력소모 분석 |

|||

| 2. 공정 구조 및 특성 | |||

|

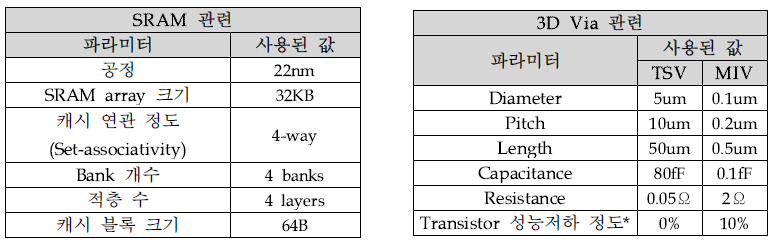

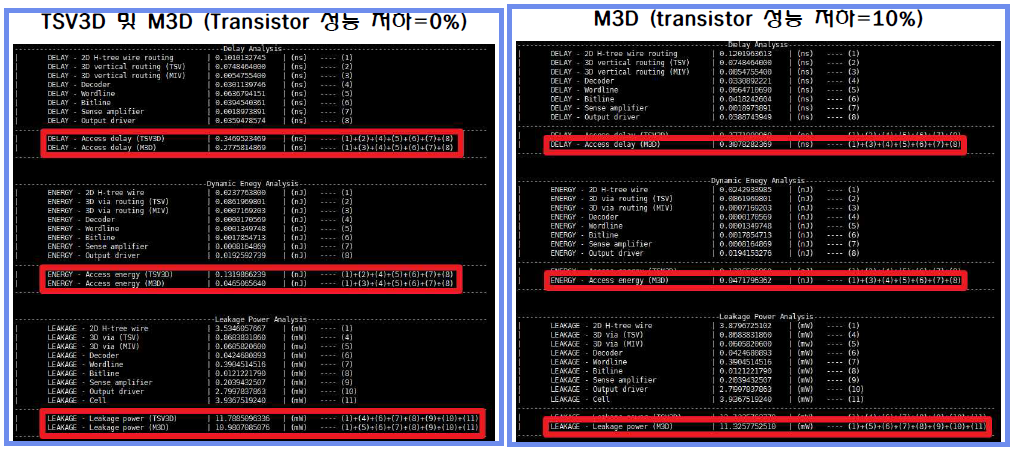

○ 공정 구조(사진 및 모식도/구조도 등) ○ 32KB 4-layer SRAM array 기준 TSV 적층구조 3D 및 M3D 구조 SRAM 분석결과 (CACTI report 사진) ▷ 공정 결과물 예시에 사용된 SRAM 및 3D via (TSV 및 MIV) 파라미터  * M3D 공정으로 인한 transistor 성능 저하의 경우, 분석 도구 내부에서 transistor 저항 값을 증가시켜서 성능 저하를 반영함  ○ 공정 특성 : ▷ 32KB 4-layer SRAM 적층 구조 |

|||

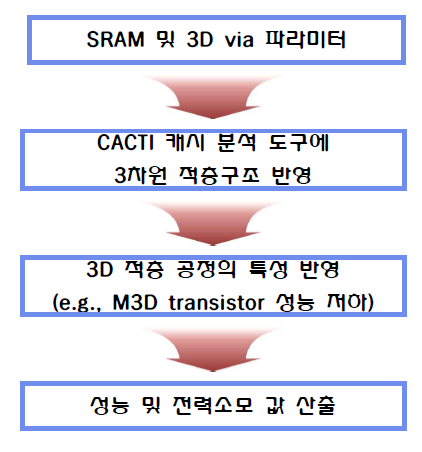

| 3. 공정순서 | |||

|

|||

| 4. 공정 조건 | |||

|

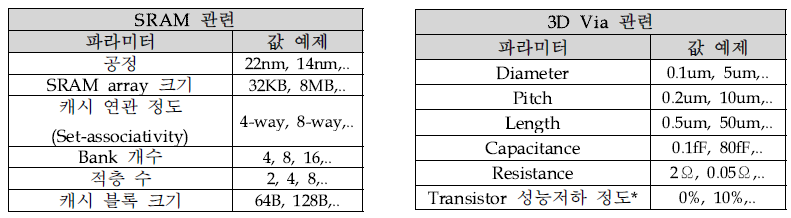

▷ 3차원 적층구조 SRAM 전력 소모 분석에 필요한 파라미터 정리  * M3D 공정 적용 시, 저온공정으로 인한 transistor 성능 저하가 발생하게 됨. Transistor 성능 저하를 몇%로 반영할지에 대한 파라미터 필요 (최근 M3D 공정 적용 시 약 10% 성능 저하 예상) ▷ 위의 표에 기재된 SRAM 및 3D Via 에 대한 파라미터를 제공받으면, 해당 파라미터를 기반으로, M3D 적층 구조를 적용했을 때 TSV 기반 3D구조 대비 전력소모 절감 정도를 분석가능 함 |

|||