| 1200V급 6인치 SiC VDMOSFET 표준공정

| 문서번호 | ETC2024001 | 작성일 | 2024. 08. 19. |

| 소속 | 포항공과대학교 나노융합기술원 | 담당자 | 한성웅 |

| 연락처 | 010-5577-3449 | 이메일 | temuchin80@nnfc.re.kr |

[ 공 정 규 격 서 ] |

|||

| 공정명 | 1200V급 6인치 SiC VDMOSFET 표준공정 | 공정분류 | 소자 |

| 1. 공정 목적 및 용도 | |||

|

○ 공정 목적: 실리콘카바이드 (SiC)의 우수한 물리적, 전기적 특성을 활용하여 실리콘 (Si) 대비 고전압 대전류 및 낮은 소비 전력 특성을 가지는 전력 소자를 대구경 6인치 웨이퍼에서 개발함. 기업지원을 목표로 한 6인치 SiC 전력소자 설계 기술과 표준 공정 기술을 확보하여 해당 분야 경쟁력 강화. ○ 용도: 전기자동차용 인버터, 가전제품, PC, 산업용 UPS, 의료기기, 태양광 인버터 등, 전기를 사용하는 다양한 제품 및 시설에 적용 |

|||

| 2. 공정 구조 및 특성 | |||

|

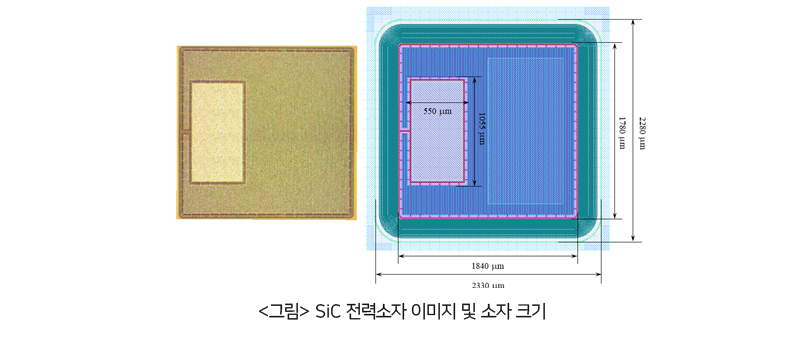

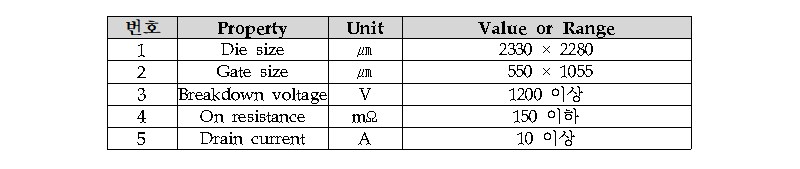

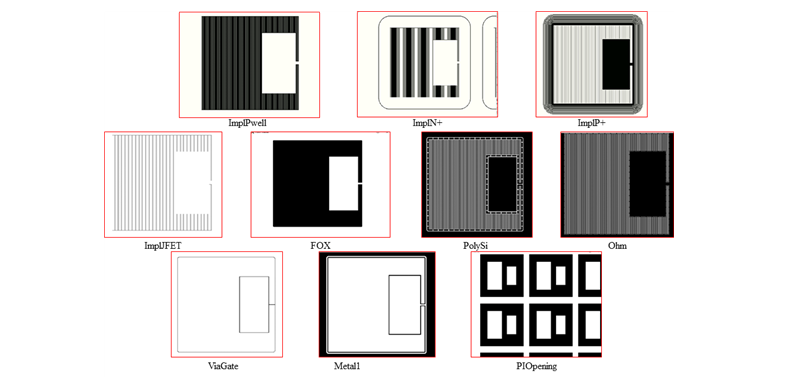

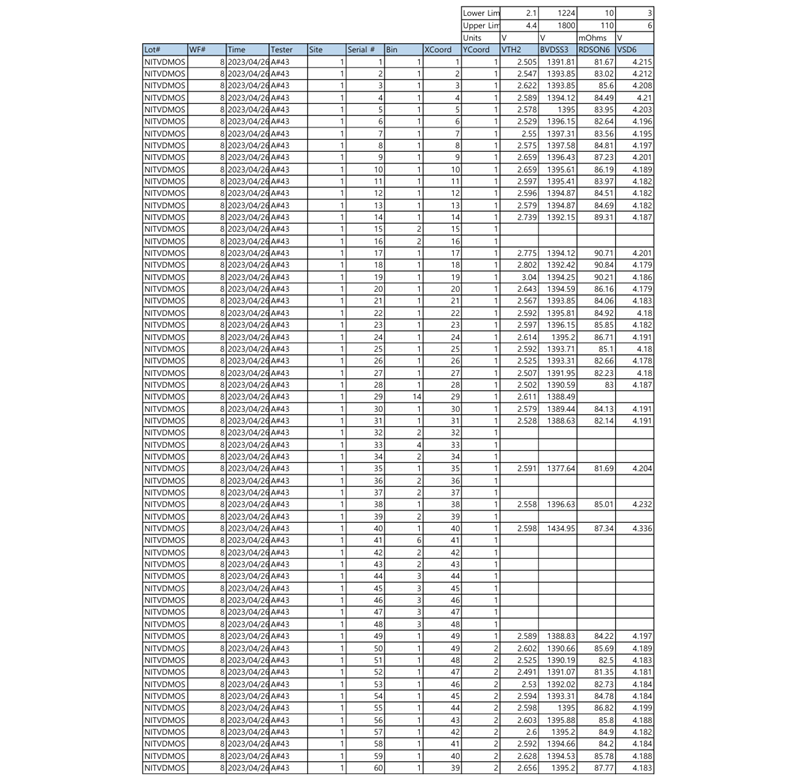

○ 사용 에피 구조 – 6 inch SiC epi wafer (MOSFET Grade) - Buffer : N-type Doping 1 × 1018/cm3 - Epi 1 : Thickness, 15 μm/Doping, 4 × 1015/cm3 - Epi 2 : Thickness, 2 μm/Doping, 1 × 1016/cm3 ○ 소자 특성 - 제작 소자 특성   - SiC VDMOSFET Layout  - Electrical Die Sorting (EDS) 후 선별된 10개 소자의 Breakdown voltage, On resistance, Drain current 특성  |

|||

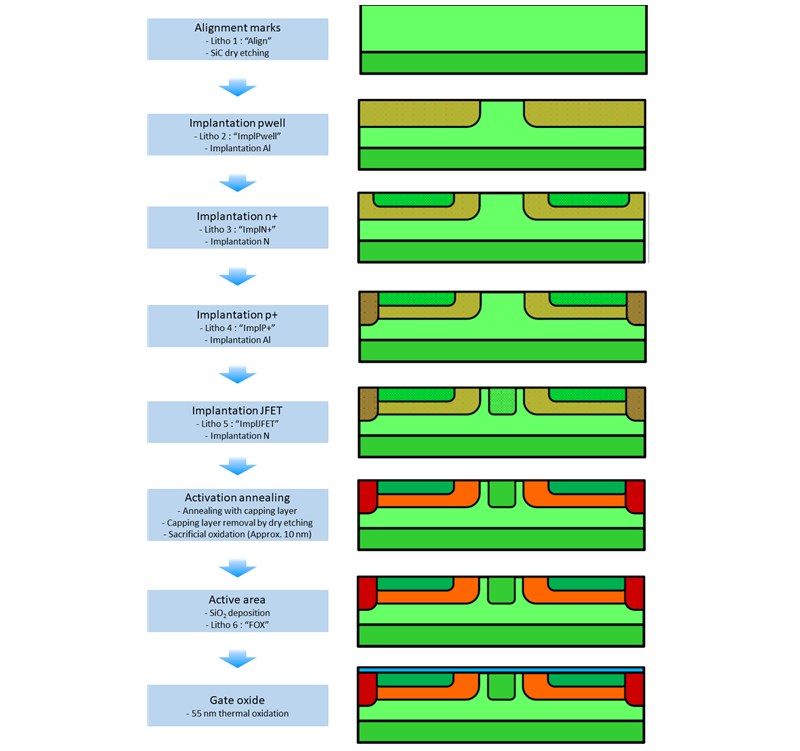

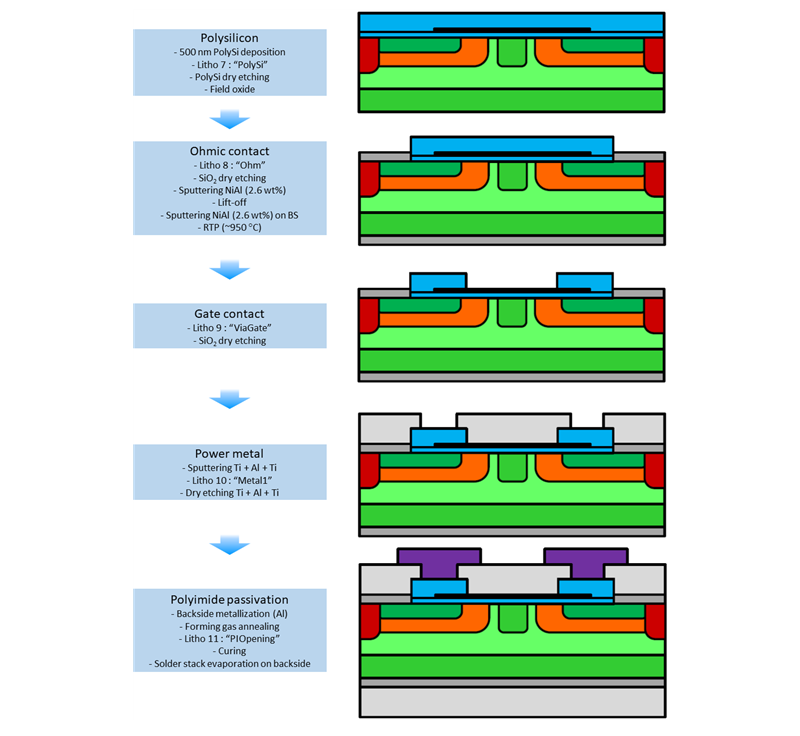

| 3. 공정순서 | |||

|

|||

| 4. 공정 조건 | |||

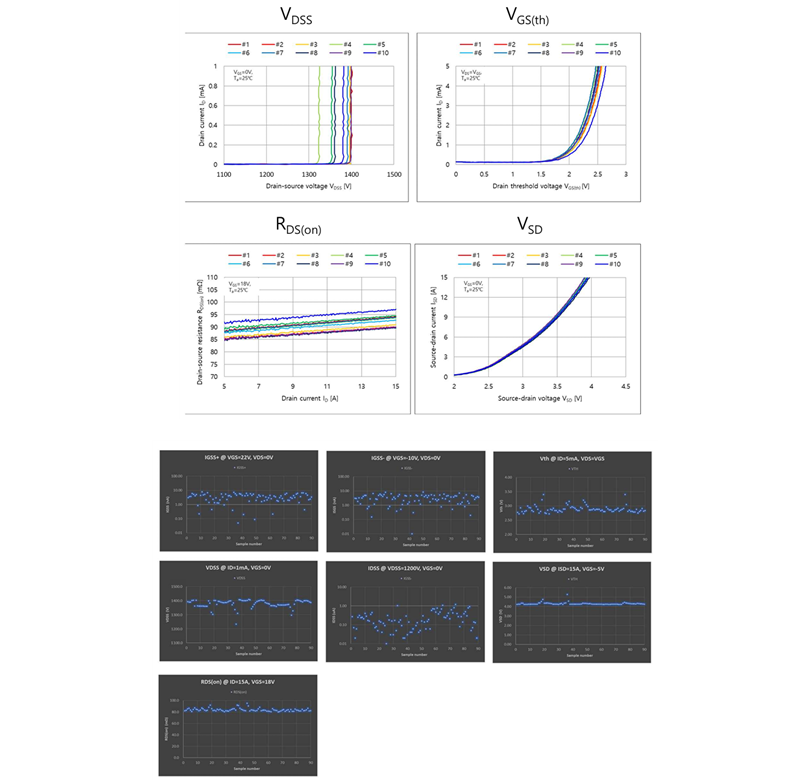

- 특성평가 Data sheet |

|||