| CMOS 공정 compatible 원자스위치 기반 논리게이트 제작 공정

| 문서번호 | SA2019004 | 작성일 | 2019. 12. 03. |

| 소속 | 성균관대학교 | 담당자 | 이성주 |

| 연락처 | 010-4597-0413 | 이메일 | leesj@skku.edu |

[ 공 정 규 격 서 ] |

|||

| 공정명 | CMOS 공정 compatible 원자스위치 기반 논리게이트 제작 공정 | 공정분류 | 소자/센서 |

| 1. 공정 목적 및 용도 | |||

| M3D 상층부에 원자스위치 소자 기반의 논리게이트를 구현하는 공정으로 CMOS 기술 기반 하에 구현된 논리게이트가 하층부의 CMOS 소자와 연결되었을 때도 정상적으로 작동하는 것이 목적임. CMOS 기술 기반 하에 구현된 논리게이트의 Bias 조건에 따른 동작 특성의 변화를 분석하고, 0.3V 이하에서 원자스위치의 동작 여부를 확인하여, 최종적으로 M3D 상층부에 논리게이트를 구현하는 공정을 확보하는데 목적이 있음. | |||

| 2. 공정 구조 및 특성 | |||

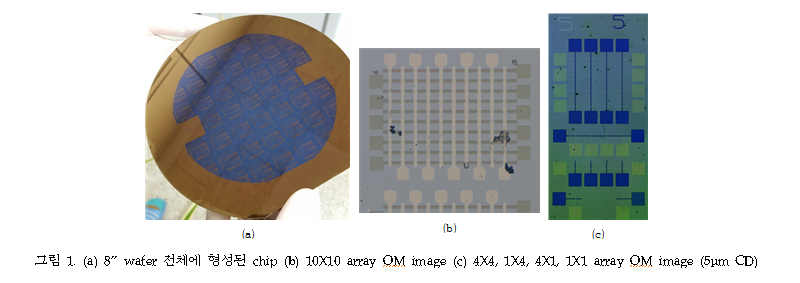

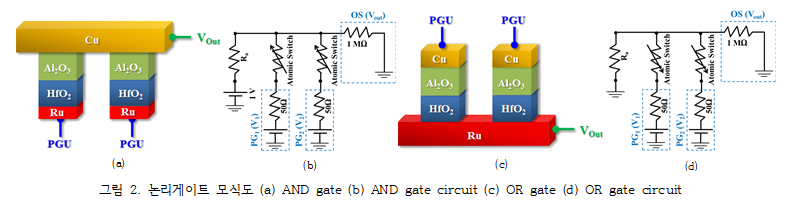

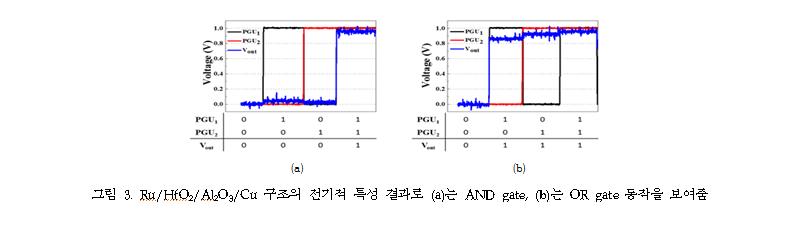

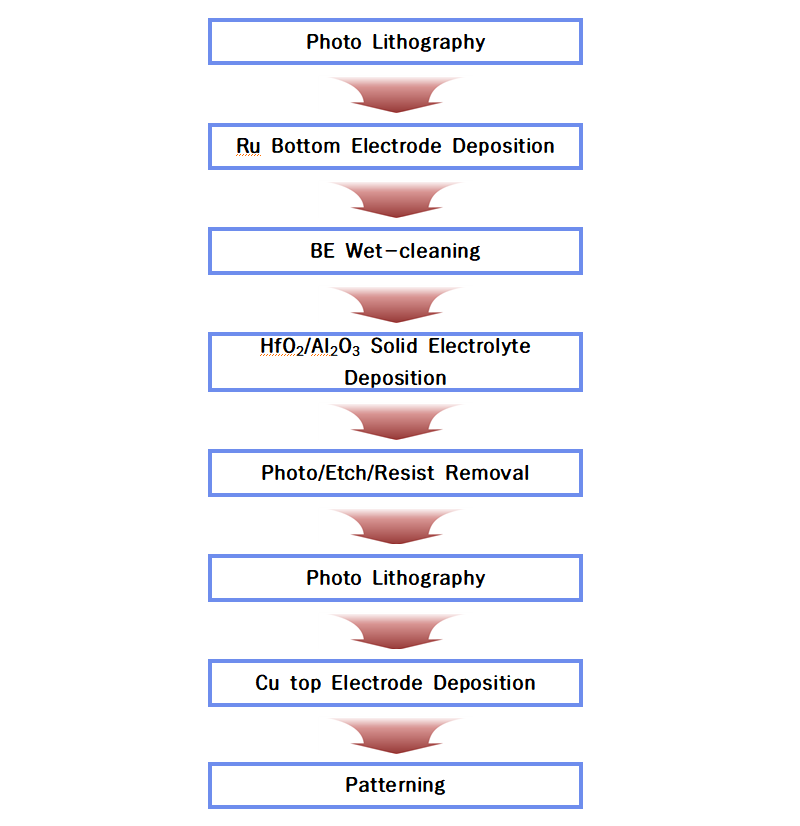

공정 결과물(사진)  그림 1(a)은 공정이 완료된 8‘’ wafer로 하나의 chip에 크기별로 10X10부터 1X1 array 형태로 소자가 형성되어 있으며, CD는 5μm임. 그림 1(b)는 하나의 chip을 optical microscopy를 이용해 찍은 이미지로 wafer 전반에 걸쳐서 5μm - 30μm으로 형성된 것을 확인할 수 있음. 그림 1(c)에서 5μm 소자를 자세히 확인할 수 있는데, 하나의 선폭에서 4X4 array, 1X4 array, 4X1 array, 1X1 array를 확인할 수 있다.  그림 2는 공정 진행 결과 논리게이트 모식도로 bottom electrode로 Ru이 사용되며, HfO2는 Active layer, Al2O3는 blocking layer로 사용된다. top electrode는 Cu를 사용해 Cu의 migration에 의해서 소자가 동작하게 된다. 공정 결과물 특성  |

|||

| 3. 공정순서 | |||

|

|||

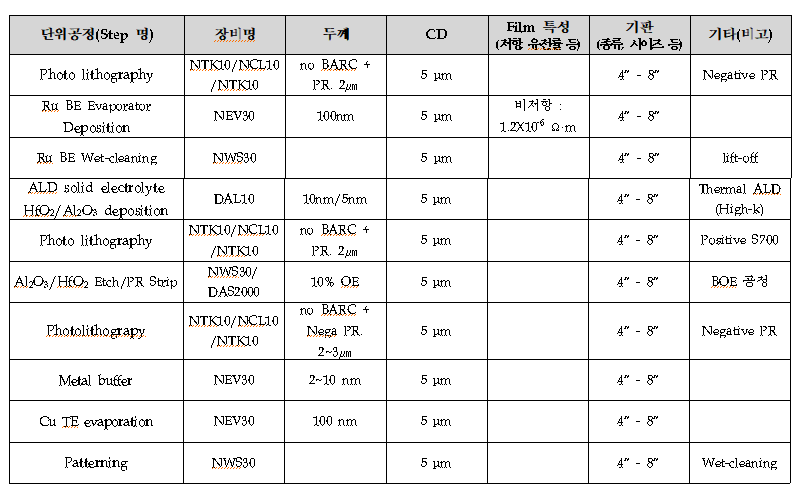

| 4. 공정 조건 | |||

|

|||