| 본딩 기반 저온 기판 및 채널층 전사

| 문서번호 | PLA01201709 | 작성일 | 2018. 12. 14. |

| 소속 | 한양대학교 | 담당자 | 최창환 |

| 연락처 | 010-8721-8062 | 이메일 | cchoi@hanyang.ac.kr |

[ 공 정 규 격 서 ] |

|||

| 공정명 | 본딩 기반 저온 기판 및 채널층 전사 | 공정분류 | 3차원 본딩 및 저온 단위 공정 |

| 1. 공정 목적 및 용도 | |||

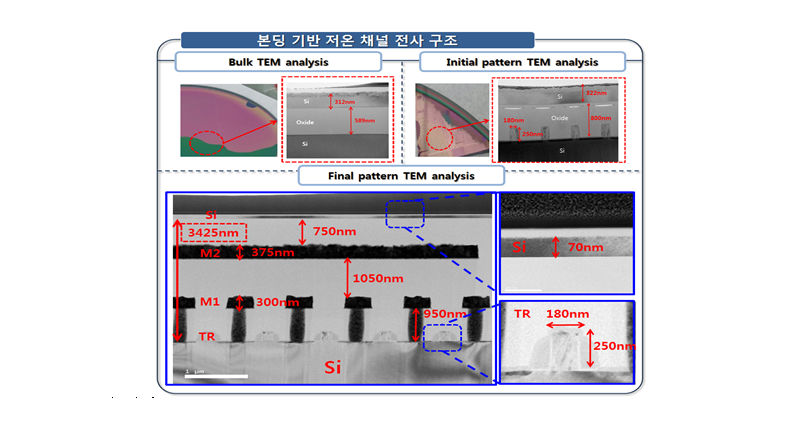

| 본딩 기반의 저온 기판 및 채널 층 전사 공정으로서 기존 TSV의 μm 급 Si 기판 및 채널층을 얇은 수백 nm급 기판을 사용하여 소비 전력을 감소 시킬 수 있는 Monolithic 3차원 적층 구조 형성을 위한 저온 플랫폼을 확보하는 목적을 가지며 이를 통해 다양한 반도체 소자, 디스플레이, 센서 및 MEMS 분야의 3차원화를 가능하게 함. | |||

| 2. 공정 구조 및 특성 | |||

|

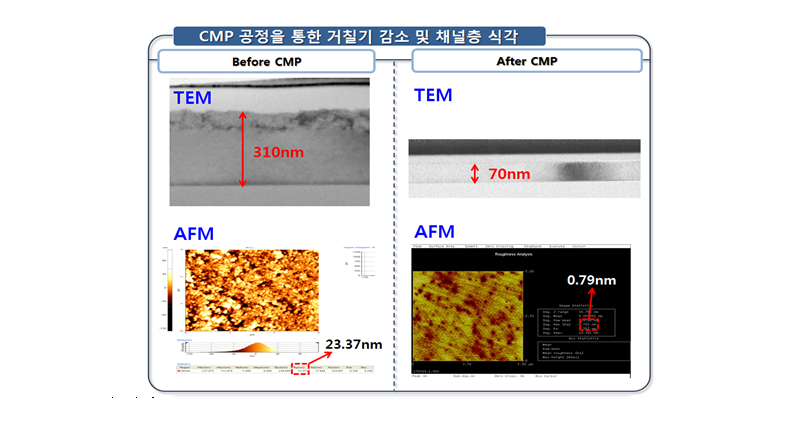

○ 공정 결과물(사진) - 저온 기반 Bulk & Pattern wafer 본딩 기판 및 소자 채널층 전사 결과  ○ 공정 결과물 특성  |

|||

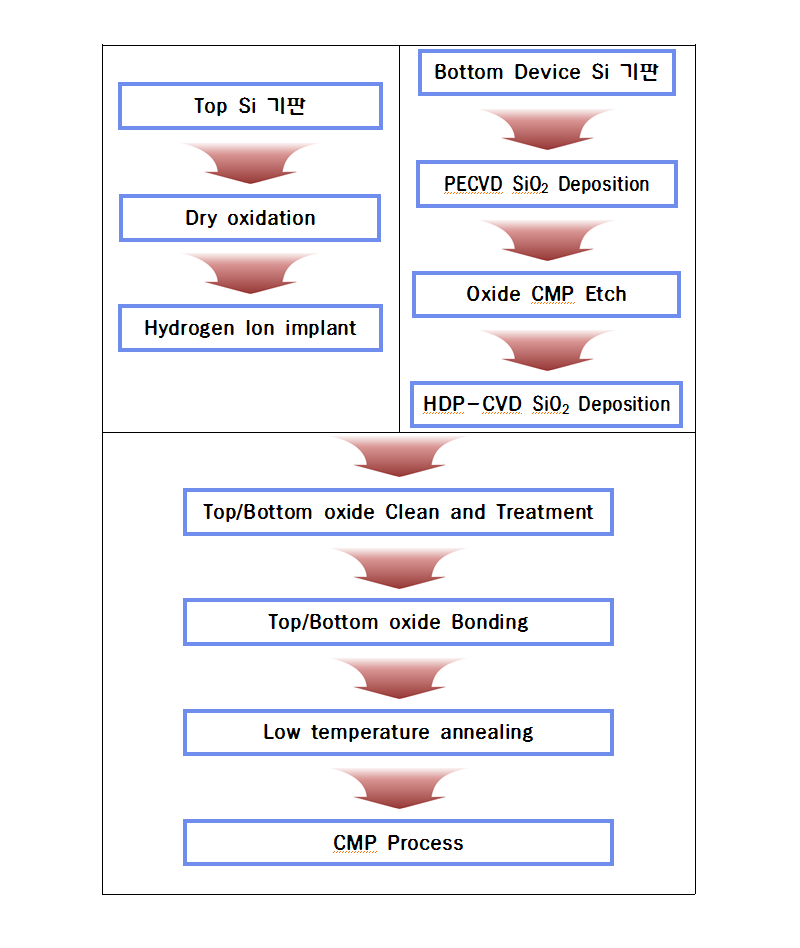

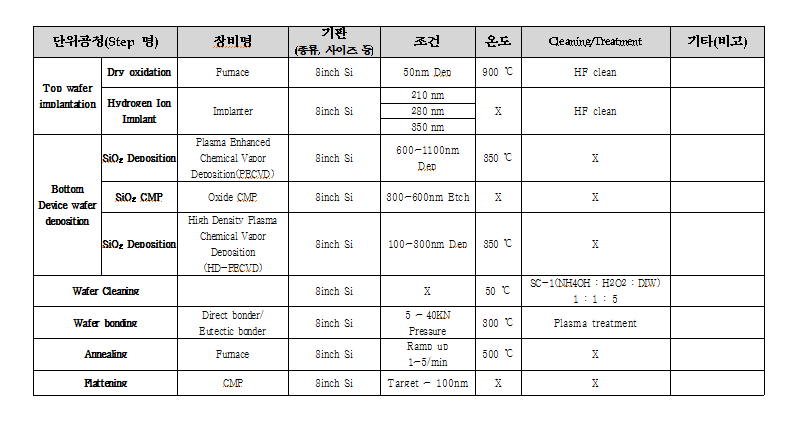

| 3. 공정순서 | |||

|

|||

| 4. 공정 조건 | |||

|

|||