| 3차원 적층 상부소자 (Relay소자) 집적 공정을 위한 저온 BEOL 공정 기술 개발

| 문서번호 | PLA02201704 | 작성일 | 2018. 04. 05. |

| 소속 | 서강대학교 | 담당자 | 권혁수 |

| 연락처 | 02-713-8467 | 이메일 | kwonhyugsu@naver.com |

[ 공 정 규 격 서 ] |

|||

| 공정명 | 3차원 적층 상부소자 (Relay소자) 집적 공정을 위한 저온 BEOL 공정 기술 개발 | 공정분류 | BEOL |

| 1. 공정 목적 및 용도 | |||

| BEOL의 top layer에 NEM relay를 제작할 수 있는 공정 기술 확보 | |||

| 2. 공정 구조 및 특성 | |||

|

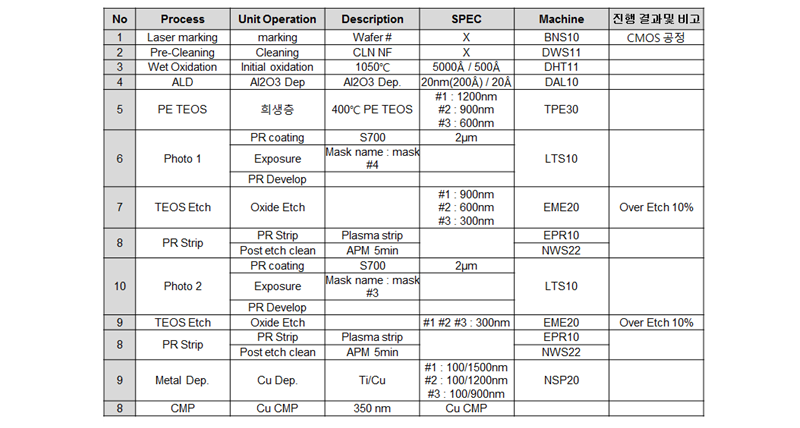

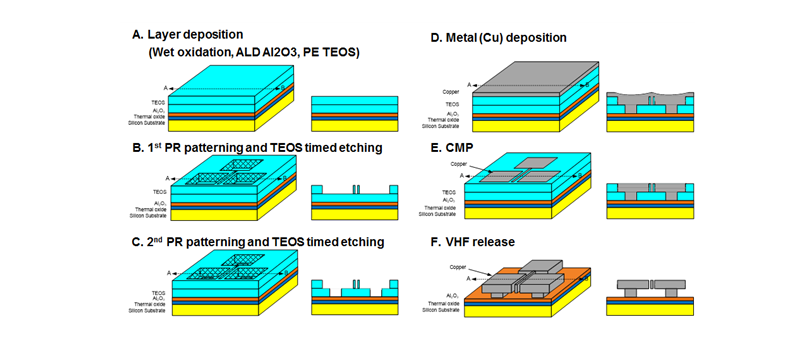

2. 공정 조건 및 brief run-sheet  3. 공정 결과물 - 500nm급 NEM 소자 패턴 공정 확보 (Stepper적용) 4. 공정 결과물 특성 ○ 3차원 적층 상부소자 (Relay 소자) 집적 공정을 위한 저온 BEOL공정 개발 - 희생층 두께: 0.42um - Electro-plating, CMP 이후 dishing 및 erosion 현상 발생하지 않음 - 공정 온도 < 550 °C ( 최대 400 °C ) |

|||

| 3. 공정순서 | |||

|

|||

| 4. 공정 조건 | |||

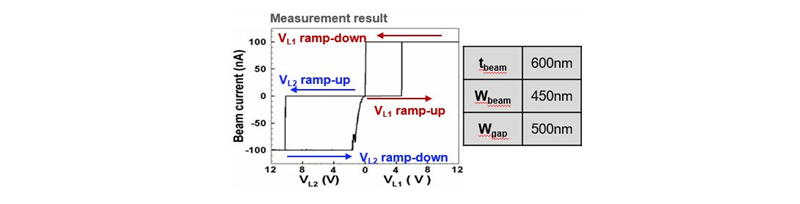

- 소자 측정 결과, simulation 대비 큰 dimension (NNFC 측 lithography 장비의 pattern 한계) 으로 인하여 예상 동작 전압보다 높게 나타남을 확인할 수 있음. - 다만, on/off ratio 는 측정 시 compliance current를 걸지 않을 시 105 이상 나타나는 것을 확인함. (일반적으로 off current 는 수 pA, on current 는 micro-welding effect 로 인하여 소자가 손상되는 것을 방지하기 위하여 1 um 근처에서 compliance current를 설정하고 측정을 진행함.) - 동작 전압은 gap scaling 진행하면 감소시킬 수 있음 - On off ratio 및 CMOS compatible process 측면에서 설정한 목표를 충족시킴 - 소자 측정 결과, simulation 대비 큰 dimension (NNFC 측 lithography 장비의 pattern 한계) 으로 인하여 예상 동작 전압보다 높게 나타남을 확인할 수 있음. - 다만, on/off ratio 는 측정 시 compliance current를 걸지 않을 시 105 이상 나타나는 것을 확인함. (일반적으로 off current 는 수 pA, on current 는 micro-welding effect 로 인하여 소자가 손상되는 것을 방지하기 위하여 1 um 근처에서 compliance current를 설정하고 측정을 진행함.) - 동작 전압은 gap scaling 진행하면 감소시킬 수 있음 - On off ratio 및 CMOS compatible process 측면에서 설정한 목표를 충족시킴

|

|||